MOS開關

開關在集成電路設計中有很多作用。在模擬電路中,開關被用來實現諸如電阻的開關仿真[1]等有用的功能。開關同樣也用于多路選擇、調制和其他許多應用。在數字電路中,開關被用做傳輸門,并加入了在標準邏輯電路沒有的尺寸的靈活性。本節的目的是研究與CMOS集成電路兼容的開關特性。

我們從電壓控制開關的特性開始。圖4.1-1所示為該器件模型。電壓vc控制開關的狀態——開或關。電壓控制開關是一個三端網絡,其中A、B端組成開關,c端是控制電壓vc作用端。開關最重要的特性是它的導通電阻roN和關斷電阻rOFF。理想情況下,rON為零而roFF為無窮大,實際上并非如此。此外,這些值與端口條件有關,絕不會是常數。通常,開關會有一些電壓偏移,圖4.1-1中用Vos模擬。Vos表示當開關為導通狀態、電流等于零時,端點A和B之間存在的小幅值電壓。IOFF表示開關為斷開狀態的漏電流。電流IAIB表示開關端點與地之間的漏電流(或其他電源電壓)。圖4.1-1中偏移源和漏電流的極性是不確定的,圖中的方向是任意標注的。在模擬采樣數據電路應用中,寄生電容是一個需認真考慮的問題。電容CA和CB是開關端A、B與地之間的寄生電容。電容CAB開關端A、B之間的寄生電容。電容CAC和CBC存在于電壓控制端C和開關端A、B之間的寄生電容。電容CAC和CBC的影響稱為電荷饋通——由此控制電壓的一部分會出現在開關A、B端。

MOS技術的一個優點是可提供一個性能良好的開關。圖4.1-2顯示了一個MOS晶體管被用做開關的情況。它的性能可以由圖4.1-1顯示的MOS晶體管大信號模型構成的開關確定。可以看到,MOS晶體管的漏極或源極做端點A或o取決于端點電壓(即,對n溝道管,如果A端電位高于B,那么A端是漏極,B端是源極)。導通電阻由rD、rs的組合與始終存在的溝道電阻串聯組成。通常rD和rs的影響很小,所以主要考慮溝道電阻。溝道電阻的表達式可這樣求得:在開關導通狀態,開關兩端的電壓很小,且VGS很大。因此,MOS器件可以假設工作在非飽和區。式(3.1-1)重寫如下以表示這個狀態:

式中,VDS比VGS - VT小,但是比零大(VDS為負時,VGS變為 VGD)。小信號溝道電阻由下式給出:

式(4.1-2)中的Q是晶體管的靜態工作點。圖4.1-3說明了n溝道管漏極電流隨漏、源電壓變化的曲線,其巾管子的寬長比WIL=5/1,VGS等間隔增加。此圖說明了MOS管下作的一些重要原理。注意,圖中的曲線并不是關于Vl=0對稱的。這是因為晶體管端(漏、源)開關起著Vl過零的轉換作用。例如,當VI為正時,B點是漏極,A點為源極,且VBS同定為-2.5V,VGS由給定的VG固定。當V1為負時,B點為源極,A點為漏極,且VI和VBS連續減少,而VGS增加,從而導致電流增加。

圖4.1-4顯示了當VDS=0.1V、W/L=1、2、5和10時rON隨VGS變化的圖。從圖中可以看出W/L越大,roN越低。當VGS減到VT(VT=0.7V)時,rON為無窮大,因為開關斷開。

當VGS小于或等于VT時,開關斷開,理想情況下rOFF為無窮大。當然,它不可能為無窮大。但因為它非常大,截止狀態的性能由漏極-體和源極-體的漏電流決定,就像亞閾值電壓區從漏到隙的漏電流一樣。從源和漏到體的漏電流主要是pn結漏電流,在圖4.1-1中用IA和IB模擬。典型情況下,漏電流在室溫下為1fA/μm2的數量級,且溫度每升高8℃而增長一倍(見例2.5-1)。

圖4.1-1中模擬的失調電壓在MOS開關中不存在,因此,在MOS開關性能中不必考慮。圖4.1-1中的電容CA、CB、CAC和CBC直接對應于MOS管的電容CBS、CBD、CGS和CCD(見圖3.2-1)。MOS管的CAB很小,通常可以忽略。

開關的一個重要方面是開關端和控制端問電壓的變化范圍。對n溝道MOS管,我們看到柵極電壓應該比源和漏極電壓大得多,以確保MOS管導通。作為p溝道管,柵極電壓應該比源和漏極電壓小得多。典型情況下,n溝道開關的體接最負值(p溝道開關的體接最高電位)。這個要求可以用n溝道開關來說明。假設柵極的導通電壓是正電源電壓VDD,體接地,保持n溝道開關導通,直到開關端信號(源、漏端電壓近似相等)接近VDD-VT。當信號達到VDD-VT時,開關開始轉向關斷。n溝道開關的典型電壓如圖4.1-5所示,其中開關被連接在兩個網絡中間。

如圖4.1-6所示,考慮利用開關為電容充電。n溝道管被用做升關,且Vφ是作用在柵極上的控制電壓(時鐘)。在電路的電荷轉移過程中,開關的導通電阻起重要作用。例如,當Vφ升高(Vφ>Vin+ VT),M1將C連接到電壓源vin此時的等效電路如圖4.1-7所示,可以看做C以時間常數rON C充電到Vin。為了有效地工作,必須滿足rON C<

考慮這樣一種情況,Vφ為高電平的時間T=0.1μS,C=0.2pF,那么導通電阻rON必須小于100kΩ才能滿足電荷轉移時間等于5倍時間常數。對于5V的時鐘擺幅和2.5V的Vin以及圖4.1-4中示出的W=L的MOS管,rON≈6.4kΩ。此值在所要求的時間內進行電荷轉移來說已足夠小。我們希望開關盡可能小(即具有最小的WxL),從而可以減小來自柵極的電荷饋通。

圖4.1-6中的開關在關斷狀態除了其漏電流之外,對電路的影響很小。圖4.1-8顯示了一個采樣保持電路,電路中漏電流可能引起嚴重問題。如果CH不夠大,那么在保持模式中MOS開關是斷開的,漏電流會使CH充上或放掉相當量的電荷。

在單片集成電路開關中,最嚴重的限制之一是時鐘饋通效應。時鐘饋通(也稱做電荷注入和電荷饋通)是由于柵到源和漏的耦合電容引起的。這個耦合會導致柵極信號(一般是時鐘)傳送到源極昶I漏極節點,這是一個雖不希望但卻不可避免的影響。電荷注入涉及一個復雜的過程,引起的影響取決于諸如晶體管的版圖、尺寸、源極和漏極節點的阻抗和柵極的波形等一系列因素。試圖對所有這些影響進行精確的分析是不可能的——我們用計算機去做!然而,對這些重要影響的定性了解仍是有用的。

考慮適合于研究電荷注入分析的簡單電路如圖4.1-9(a)所示。圖4.1-9(b)給出了管子的模型,用電阻Rchannel和Cchannel表示溝道電阻和柵-溝道耦合電容。Cchannel和Rchannel值取決于器件(的端口情況。溝道中的分布電阻用Rchannel表示。除溝道電容外還有交疊電容CGSO和CGDO。為了近似計算總溝道電容,可如圖4.1-9(c)所示將耦合電容分成兩個相等的部分并入柵—源端和柵-漏端。這樣的處理是有益的。

圖4.1-9電路中,電荷隨著管子柵極電壓φ1高到低的跳變而產牛的注入是令人感興趣的。此外,考慮柵電壓過渡的兩種情況(快躍變時間和慢躍變時間)很方便。首先考慮慢躍變情況(慢和快的意思很快將會介紹)。當柵極電壓降低時,有電荷注入溝道。但是最初管子保持導通狀態,所以無論怎樣,注入的電荷只在輸入電壓源VS中流動,不會出現在負載電容CL上。隨著柵極電壓降低到某一點,管子截止(當柵極電壓達到VS+VT時)。當管子截止時,注入電荷除了流進CL之外沒有其他路徑可走。

對于快躍變的情況,與溝道電阻和溝道電容有關的時間常數限制著流向電壓源的電荷量,因此當晶體管處于導通狀態時,一些注入的溝道電荷就提供給CL以影響其匕的總電荷。

為了對快慢情況有更進一步的了解,將柵極電壓模擬為分段恒定波形(一個量化波形)并考慮每個跳變過程中電荷的流動,如圖4.1-10所示。圖中,所示的CL電壓的變化范圍表示管子導通時的工作情況。在兩種情況中,量化的電壓步長是相同的,但是步長間的時間是不同的。CL兩端電壓是呈指數變化的,其時間常數由溝道電阻和溝道電容決定,并不隨快、慢情況而改變。

分析表達式可以得出對管子在快慢情況下工作的近似描述[2]。考慮柵極電壓從VH到VL的變化(即5.0V到0.0V),其在時域中可以描述為:

這里的U是VG(t)的斜率。工作在慢躍變時由以下關系所確定:

這里VHT定義為:

由電荷注入引起的誤差(所希望的電壓Vs和實際電壓VcL之間的差)由下式描述:

在快開關情況下由下列關系確定:

誤差電壓給出為:

下面的例子說明由式(4.1-3)到式(4.1-8)所給出的電荷饋通模擬的應用。

例4.1-1 電荷饋通誤差的計算

計算圖4.1-9所示電路中電荷饋通的影響。其中Vs=1.0V,CL=200fF,W/L=0.8μm/0.8μm,VG有兩種情況見下圖的說明。模型參數見表3.1-2和表3.2-1。忽略AL和△W的影響。

解:

情況1:第一步要確定表達式中U的值:

在0.2ns之后,從5V跳變到OV,U=25x109V/s。

為了確定工作狀態,必須首先驗證下面的關系:

觀察到在晶體管開關上有反向偏置影響VT,VHT為:

因此給出:

所以為快速狀態。

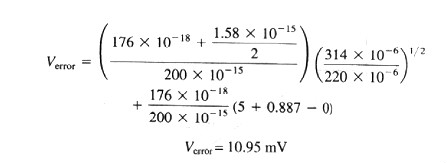

由快速狀態應用式(4.1-8)得:

情況2:第一步要確定表達式中U的值:

在10 ns之后從5V降到OV時,U=5xl08,于是按照下面的測試表明是慢速狀態:

這個例子說明了電荷饋通模型的應用。讀者應該得到警示,不要期望從式(4.1-3)到式(4.1-8)得到實際電路中關于電荷饋通量的精確答案。這個模型只是有助于了解各種電路元件和端口條件的影響,以便在最小化設計中出現不希望有的現象。

采用圖4.1-11所示的技術有可能部分抵消饋通效應。在這里虛擬MOS管MD(這里源和漏被接到信號線,柵極接反相時鐘端、)被用來提供與Ml反相的時鐘饋人。MD的面積可以被設計成提供最小的時鐘饋通。但遺憾的是,這個辦法不可能完全消除饋通,并且在某些情況下還會更糟。另外還必須提供一個反相時鐘作用到虛擬開關上。可以通過采用最大可能的電容、相對較小幾何尺寸的開關和保持盡可能小的時鐘擺幅來減少時鐘饋通。通常,這些解決方案會在其他方面產生問題,這就需要進行一些折中。

單溝道MOS升關導致的動態范網限制可以采用圖4.1-12所示的CMOS開關加以避免。使用CMOS技術,開關通常由如圖所示的、并聯的p溝道和n溝道增強型管構成。在這種結構中,當φ值為低時,兩只管子均截止,實現一個有效的開路。當φ值為高時,兩只管子均導通,給出一個低阻抗狀態。p溝道管和n溝道管的體分別連接至最高和最低電位。CMOS開關優于單溝道MOS開關的主要方面是在導通狀態下模擬信號的動態范圍明顯增加。

在圖4.1-13中模擬信號動態范圍的增加是顯然的,圖中畫出了CMOS開關導通電阻作為輸入電壓函數的變化關系。此圖中,p溝道管和n溝道管的尺寸這樣來設置,以至于在相同端口條件下有等效的電阻。雙峰性能是由于當Vin為低電平時,n溝道管起主導作用,而Vin為高電平(接近VDD)時p溝道管起主導作用。在中間(VDD/2附近),兩個管子的并聯導致出現最低值。中間的凹點是由于遷移率降低的影響,在用LEVEL 1模型分析時并不明顯。

在本節中,我們已經看到MOS管可以構成積分電路中最好的開關之一。它們只需要很小的面積,非常低的功耗,并且在多數應用中能夠提供合理的rON和roFF值。把適宜的開關實現放進設計者的基本設計模塊中將產生一些有趣和有用的電路及系統,這些將在以后幾章介紹。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

關注KIA半導體工程專輯請搜微信號:“KIA半導體”或點擊本文下方圖片掃一掃進入官方微信“關注”

長按二維碼識別關注