MOS晶體管種類

_按溝道區中載流子類型分

N溝MOS晶體管:襯底為P型,源漏為重摻雜的N+,溝道中 載流子為電子

P溝MOS晶體管:襯底為N型,源漏為重摻雜的P+,溝道中載流子為空穴

在正常情況下,只有一種類型的載流子在工作,因此也稱其為單極晶體管

-按工作模式分

增強型晶體管:若在零柵壓下不存在漏源導電溝道,為了形成導電溝道,需要施加一定的柵壓,也就是說溝道要通過“增強”才能導通

耗盡型晶體管:器件本身在漏源之間就存在導電溝道,即使在零柵壓下器件也是導通的。若要使器件截止,就必須施加柵壓使溝道耗盡

MOS晶體管特性

假定漏端電壓Vds為正,當柵上施加一個小于開啟電壓的正柵壓時,柵氧下面的P型表面區的空穴被耗盡,在硅表面形成一層負電荷,這些電荷被稱為耗盡層電荷Qb。這時的漏源電流為泄漏電流。

如果Vgs>Vth,在P型硅表面形成可移動的負電荷Qi層,即導電溝道。

由于表面為N型的導電溝道與P型襯底的導電類型相反,因此該表面導電溝道被稱為反型層。

MOS村底偏置效應

當襯底施加偏壓時,勢壘高度的增加導致耗盡區寬度的增加,因此對于給定的Vgs和Vds,Vbs的增加會使Ids減小。這是因為Vbs增加,體電荷Qb增加,而Vgs和Vds不變,由于柵電荷Qg固定,根據電荷守恒定律Qg=Qi+Qb,所以Qi反型層電荷減少,因此電導減少。

而這時,如果要使MOS晶體管開啟即進入強反型區,就是反型層電荷相應的增加那就耍提高柵電壓,增加柵電荷。所以當MOS襯底施加偏壓時,MOS晶體管的開啟電壓會升高。

MOS熱載流子效應

當溝道長度減小,同時保持電源電壓不變,溝道區靠近漏端附近的最大電場增加。隨著載流子從源向漏移動,它們在漏端高電場區將得到足夠的動能,引起碰撞電離,一些載流子甚至能克服Si-Si02界面勢壘進入氧化層,這些高能載流子不再保持它們在晶格中的熱平衡狀態,并且具高于熱能的能量,因此稱它們為熱載流子。對于正常工作中的MOSFET,溝道中的熱載流子引起的效應稱為熱載流子效應。

當發生碰撞時,熱載流子將通過電離產生次級電子一空穴對,其中電子形成了從漏到源的電流,碰撞產生的次級空穴將漂移到襯底區形成襯底電流Ib。通過測量Ib可以很好地監控溝道熱載流子和漏區電場的情況。

由于Si-Si02的界面勢壘較高,注入到柵氧化層中的熱載流子與碰撞電離產生的熱載流子相比非常少,因此柵電流比襯底電流要低幾個數量級。

熱載流子注入到柵氧層中還會引起其它的一些效應,主要有

(1)熱載流子被Si02中電激活的缺陷俘獲,是氧化層中的固定電荷密度Qot改變; (2)在Si-Si02界面產生界面電荷Qit。由于Qot和Qit引起的電荷積累將在溝道形成阻礙載流子運動的勢壘;同時界面電荷也會增強界面附近電子的庫侖散射,使遷移率降低。因此經過一段時間的積累,以上效應會使器件的性能退化,影響集成電路的可靠性,所以應設法避免熱載流子效應。

MOS晶體管的構造與符號

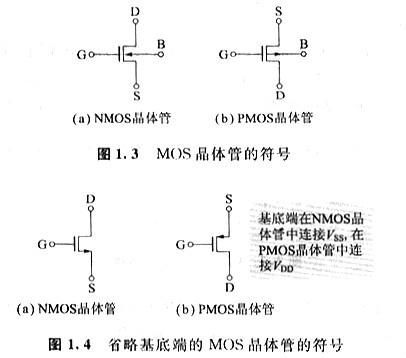

MOS晶體管的符號示于圖1.3。(KIA)MOS晶體管是四端器件:源極(S)、柵極(G)、漏極(D),以及基底端(B)。基底端在NMOS晶體管中通常銜接電路的負端電源電壓Vss,在PMOS晶體管中銜接電路的正端電源電壓VDD。電路圖中通常省略基底端(B)而采用圖1.4所示的符號。兩者的關系如圖1.5所示。

圖1.6是NMOS晶體管的構造表示圖。P型硅襯底上構成兩個n+區域,一個是源區,另一個是漏區。柵極是由摻入高濃度雜質的低電阻多晶硅(poly-crystal-linc silicon)構成。

在柵極與硅襯底間構成一層氧化膜( Si02),叫做柵氧化膜。P型硅襯底也叫做基板。

NMOS的基底銜接VSS負端電源電壓。例如,在正的電源電壓VDD為3V,負的電源電壓VSS為OV的電路中工作時,基底銜接OV(圖1.7)。

畫電路圖時,NMOS晶體管是漏極在上、源極在下,而PMOS晶體管是源極在上、漏極在下。圖1.8示出電流活動的方向和電極間的電壓。柵極—源極間電壓用VGS(PMOS晶體管中用VSG)表示,漏極—源極間電壓用VDS(PMOS晶體管中VSD)表示。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

關注KIA半導體工程專輯請搜微信號:“KIA半導體”或點擊本文下方圖片掃一掃進入官方微信“關注”

長按二維碼識別關注