mos管導通電阻

mos管導通特性與條件

(一)mos管導通特性

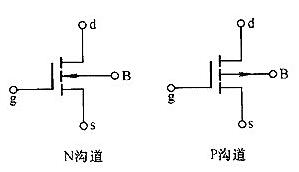

金屬-氧化層半導體場效晶體管,簡稱金氧半場效晶體管(Metal-Oxide-Semiconductor Field-Effect Transistor MOSFET)是一種可以廣泛使用在模擬電路與數字電路的場效晶體管(field-effect transistor)。MOSFET依照其“通道”的極性不同,可分為“N型”與“P型”的MOSFET,通常又稱為NMOSFET與PMOSFET,其他簡稱尚包括NMOS?FET、PMOSFET、nMOSFET、pMOSFET等。

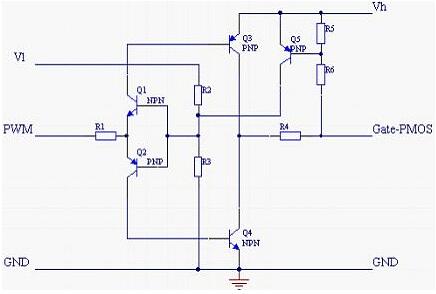

導通的意思是作為開關,相當于開關閉合。NMOS的特性,Vgs大于一定的值就會導通,適合用于源極接地時的情況(低端驅動),只要柵極電壓達到4V或10V就可以了。PMOS的特性,Vgs小于一定的值就會導通,使用與源極接VCC時的情況(高端驅動)。但是,雖然PMOS可以很方便地用作高端驅動,但由于導通電阻大,價格貴,替換種類少等原因,在高端驅動中,通常還是使用NMOS。

(二)MOS管導通條件

場效應管的導通與截止由柵源電壓來控制,對于增強型場效應管來說,N溝道的管子加正向電壓即導通,P溝道的管子則加反向電壓。一般2V~4V就可以了。但是,場效應管分為增強型(常開型)和耗盡型(常閉型),增強型的管子是需要加電壓才能導通的,而耗盡型管子本來就處于導通狀態,加柵源電壓是為了使其截止。

開關只有兩種狀態通和斷,三極管和場效應管工作有三種狀態,1、截止,2、線性放大,3、飽和(基極電流繼續增加而集電極電流不再增加)。使晶體管只工作在1和3狀態的電路稱之為開關電路,一般以晶體管截止,集電極不吸收電流表示關;以晶體管飽和,發射極和集電極之間的電壓差接近于0V時表示開。開關電路用于數字電路時,輸出電位接近0V時表示0,輸出電位接近電源電壓時表示1。所以數字集成電路內部的晶體管都工作在開關狀態。 場效應管按溝道分可分為N溝道和P溝道管(在符號圖中可看到中間的箭頭方向不一樣)。

按材料分可分為結型管和絕緣柵型管,絕緣柵型又分為耗盡型和增強型,一般主板上大多是絕緣柵型管簡稱MOS管,并且大多采用增強型的N溝道,其次是增強型的P溝道,結型管和耗盡型管幾乎不用。場效應晶體管(Field Effect Transistor縮寫(FET))簡稱場效應管.由多數載流子參與導電,也稱為單極型晶體管.它屬于電壓控制型半導體器件.場效應管是利用多數載流子導電,所以稱之為單極型器件,而晶體管是即有多數載流子,也利用少數載流子導電,被稱之為雙極型器件.有些場效應管的源極和漏極可以互換使用,柵壓也可正可負,靈活性比晶體管好。

mos管導通電阻的作用

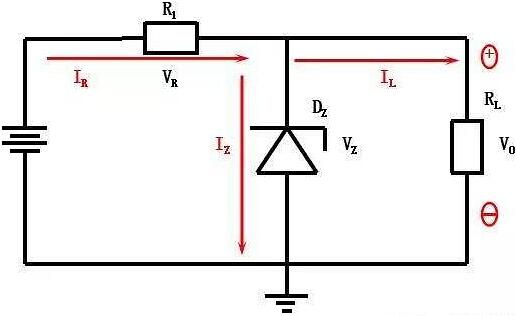

mos管導通電阻,一般在使用MOS時都會遇到柵極的電阻選擇和使用問題,但有時對這個電阻很迷茫,現介紹一下它的作用:

1.是分壓作用

2.下拉電阻是盡快泄放柵極電荷將MOS管盡快截止

3.防止柵極出現浪涌過壓(柵極上并聯的穩壓管也是防止過壓產生)

4.全橋柵極電阻也是同樣機理,盡快泄放柵極電荷,將MOS管盡快截止。避免柵極懸空,懸空的柵極MOS管將會導通,導致全橋短路

5.驅動管和柵極之間的電阻起到隔離、防止寄生振蕩的作用

降低高壓MOS管導通電阻的原理與方法

1.不同耐壓的MOS管的導通電阻分布。不同耐壓的MOS管,其導通電阻中各部分電阻比例分布也不同。如耐壓30V的MOS管,其外延層電阻僅為總導通電阻的29%,耐壓600V的MOS管的外延層電阻則是總導通電阻的96.5%。

由此可以推斷耐壓800V的MOS管的導通電阻將幾乎被外延層電阻占據。欲獲得高阻斷電壓,就必須采用高電阻率的外延層,并增厚。這就是常規高壓MOS管結構所導致的高導通電阻的根本原因。

2.降低高壓MOS管導通電阻的思路。增加管芯面積雖能降低導通電阻,但成本的提高所付出的代價是商業品所不允許的。引入少數載流以上兩種辦法不能降低高壓MOS管的導通電阻,所剩的思路就是如何將阻斷高電壓的低摻雜、高電阻率區域和導電通道的高摻雜、低電阻率分開解決。如除導通時低摻雜的高耐壓外延層對導通電阻只能起增大作用外并無其他用途。

這樣,是否可以將導電通道以高摻雜較低電阻率實現,而在MOS管關斷時,設法使這個通道以某種方式夾斷,使整個器件耐壓僅取決于低摻雜的N-外延層。基于這種思想,1988年INFINEON推出內建橫向電場耐壓為600V的COOLMOS管,使這一想法得以實現。內建橫向電場的高壓MOS管的剖面結構及高阻斷電壓低導通電阻的示意圖如圖所示。

與常規MOS管結構不同,內建橫向電場的MOS管嵌入垂直P區將垂直導電區域的N區夾在中間,使MOS管關斷時,垂直的P與N之間建立橫向電場,并且垂直導電區域的N摻雜濃度高于其外延區N-的摻雜濃度。

當VGS<VTH時,由于被電場反型而產生的N型導電溝道不能形成,并且D,S間加正電壓,使MOS管內部PN結反偏形成耗盡層,并將垂直導電的N區耗盡。這個耗盡層具有縱向高阻斷電壓,如圖(b)所示,這時器件的耐壓取決于P與N-的耐壓。因此N-的低摻雜、高電阻率是必需的。

MOS管導通過程

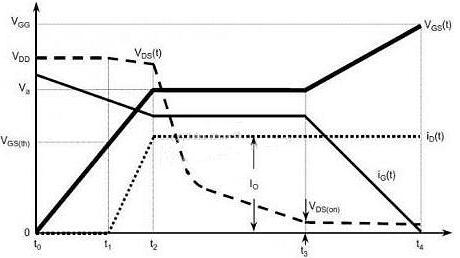

導通時序可分為to~t1、t1~t2、 t2~t3 、t3~t4四個時間段,這四個時間段有不同的等效電路。

1. t0-t1:C GS1 開始充電,柵極電壓還沒有到達V GS(th),導電溝道沒有形成,MOSFET仍處于關閉狀態。

2. [t1-t2]區間, GS間電壓到達Vgs(th),DS間導電溝道開始形成,MOSFET開啟,DS電流增加到ID, Cgs2 迅速充電,Vgs由Vgs(th)指數增長到Va。

3.[t2-t3]區間,MOSFET的DS電壓降至與Vgs相同,產生Millier效應,Cgd電容大大增加,柵極電流持續流過,由于C gd 電容急劇增大,抑制了柵極電壓對Cgs 的充電,從而使得Vgs 近乎水平狀態,Cgd 電容上電壓增加,而DS電容上的電壓繼續減小。

4. [t3-t4]區間,至t3時刻,MOSFET的DS電壓降至飽和導通時的電壓,Millier效應影響變小,Cgd 電容變小并和Cgs 電容一起由外部驅動電壓充電, Cgs 電容的電壓上升,至t4時刻為止.此時C gs 電容電壓已達穩態,DS間電壓也達最小,MOSFET完全開啟。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助