低功耗mos管

什么是低功耗

隨著計算機技術和微電子技術的迅速發展,嵌入式系統應用領域越來越廣泛。節能是全球化的熱潮,如計算機里的許多芯片過去用5V供電,現在用3.3V、1.8V,并提出了綠色系統的概念。很多廠商很注重微控制器的低功耗問題。電路與系統的低功耗設計一直都是電子工程技術人員設計時需要考慮的重要因素。

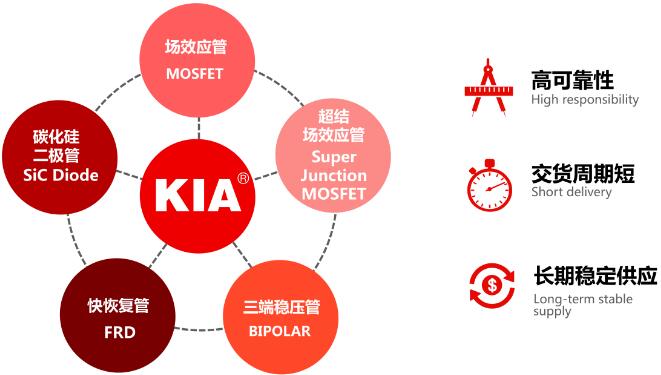

低功耗mos管原廠介紹

介紹低功耗mos管供應商信息,深圳市可易亞半導體科技有限公司.是一家專業從事中、大、功率場效應管(MOSFET)、快速恢復二極管、三端穩壓管開發設計,集研發、生產和銷售為一體的國家高新技術企業。

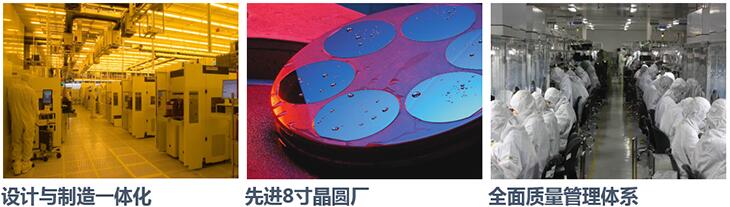

2005年在深圳福田,KIA半導體開啟了前行之路,注冊資金1000萬,辦公區域達1200平方,已經擁有了獨立的研發中心,研發人員以來自韓國(臺灣)超一流團隊,可以快速根據客戶應用領域的個性來設計方案,同時引進多臺國外先進設備,業務含括功率器件的直流參數檢測、雪崩能量檢測、可靠性實驗、系統分析、失效分析等領域。強大的研發平臺,使得KIA在工藝制造、產品設計方面擁有知識產權35項,并掌握多項場效應管核心制造技術。自主研發已經成為了企業的核心競爭力。

強大的研發平臺,使得KIA在工藝制造、產品設計方面擁有知識產權35項,并掌握多項場效應管核心制造技術。自主研發已經成為了企業的核心競爭力。

KIA半導體的產品涵蓋工業、新能源、交通運輸、綠色照明四大領域,不僅包括光伏逆變及無人機、充電樁、這類新興能源,也涉及汽車配件、LED照明等家庭用品。KIA專注于產品的精細化與革新,力求為客戶提供最具行業領先、品質上乘的科技產品。

從設計研發到制造再到倉儲物流,KIA半導體真正實現了一體化的服務鏈,真正做到了服務細節全到位的品牌內涵,我們致力于成為場效應管(MOSFET)功率器件領域的領跑者,為了這個目標,KIA半導體正在持續創新,永不止步!

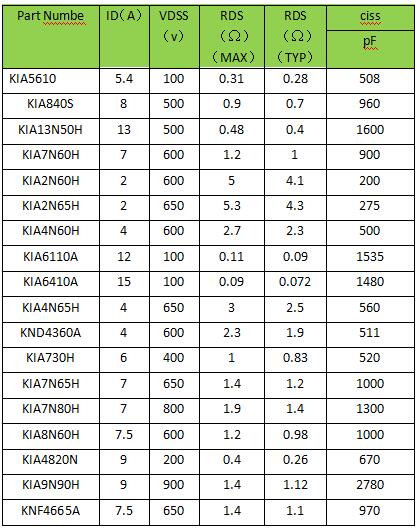

低功耗mos管選型及參數參考資料

注:這里只列出了部分低功耗mos管型號,需了解更多型號及參數資料,請聯系我們!

技術路線

目前的低功耗設計主要從芯片設計和系統設計兩個方面考慮。隨著半導體工藝的飛速發展和芯片工作頻率的提高,芯片的功耗迅速增加,而功耗增加又將導致芯片發熱量的增大和可靠性的下降。因此,功耗已經成為深亞微米集成電路設計中的一個重要考慮因素。為了使產品更具競爭力,工業界對芯片設計的要求已從單純追求高性能、小面積轉為對性能、面積、功耗的綜合要求。而微處理器作為數字系統的核心部件,其低功耗設計對降低整個系統的功耗具有重要的意義。

在嵌入式系統的設計中,低功耗設計(Low-Power Design)是許多設計人員必須面對的問題,其原因在于嵌入式系統被廣泛應用于便攜式和移動性較強的產品中去,而這些產品不是一直都有充足的電源供應,往往是靠電池來供電,所以設計人員從每一個細節來考慮降低功率消耗,從而盡可能地延長電池使用時間。事實上,從全局來考慮低功耗設計已經成為了一個越來越迫切的問題。

低功耗mos管-IC低功耗設計

微處理器的低功耗設計技術,首先必須了解它的功耗來源。其中時鐘單元(Clock)功耗最高,因為時鐘單元有時鐘發生器、時鐘驅動、時鐘樹和鐘控單元的時鐘負載;數據通路(Datapath)是僅次于時鐘單元的部分,其功耗主要來自運算單元、總線和寄存器堆。除了上述兩部分,還有存儲單元(Memory),控制部分和輸入/輸出(Control,I/O)。存儲單元的功耗與容量相關。

MOS管電路功耗主要由3部分組成:電路電容充放電引起的動態功耗,結反偏時漏電流引起的功耗和短路電流引起的功耗。其中,動態功耗是最主要的,占了總功耗的90%以上。

常用的低功耗設計技術

低功耗設計足一個復雜的綜合性課題。就流程而言,包括功耗建模、評估以及優化等;就設計抽象層次而言,包括自系統級至版圖級的所有抽象層次。同時,功耗優化與系統速度和面積等指標的優化密切相關,需要折中考慮。下面討論常用的低功耗設計技術。

1) 動態電壓調節

動態功耗與工作電壓的平方成正比,功耗將隨著工作電壓的降低以二次方的速度降低,因此降低工作電壓是降低功耗的有力措施。但是,僅僅降低工作電壓會導致傳播延遲加大,執行時間變長。然而,系統負載是隨時間變化的,因此并不需要微處理器所有時刻都保持高性能。動態電壓調節DVS(Dynarnic Voltage Scaling)技術降低功耗的主要思路是根據芯片工作狀態改變功耗管理模式,從而在保證性能的基礎上降低功耗。在不同模式下,工作電壓可以進行調整。為了精確地控制DVS,需要采用電壓調度模塊來實時改變工作電壓,電壓調度模塊通過分析當前和過去狀態下系統工作情況的不同來預測電路的工作負荷。

2) 門控時鐘和可變頻率時鐘

在微處理器中,很大一部分功耗來自時鐘。時鐘是惟一在所有時間都充放電的信號,而且很多情況下引起不必要的門的翻轉,因此降低時鐘的開關活動性將對降低整個系統的功耗產牛很大的影響。門控時鐘包括門控邏輯模塊時鐘和門控寄存器時鐘。門控邏輯模塊時鐘對時鐘網絡進行劃分,如果在當前的時鐘周期內,系統沒有用到某些邏輯模塊,則暫時切斷這些模塊的時鐘信號,從而明顯地降低開關功耗。采用“與”門實現的時鐘控制電路。門控寄存器時鐘的原理是當寄存器保持數據時,關閉寄存器時鐘,以降低功耗。然而,門控時鐘易引起毛刺,必須對信號的時序加以嚴格限制,并對其進行仔細的時序驗證。

另一種常用的時鐘技術就是可變頻率時鐘。它根據系統性能要求,配置適當的時鐘頻率以避免不必要的功耗。門控時鐘實際上是可變頻率時鐘的一種極限情況(即只有零和最高頻率兩種值),因此,可變頻率時鐘比門控時鐘技術更加有效,但需要系統內嵌時鐘產生模塊PLL,增加了設計復雜度。去年Intel公司推出的采用先進動態功耗控制技術的Montecito處理器,就利用了變頻時鐘系統。該芯片內嵌一個高精度數字電流表,利用封裝上的微小電壓降計算總電流;通過內嵌的一個32位微處理器來調整主頻,達到64級動態功耗調整的目的,大大降低了功耗。

3) 并行結構與流水線技術

并行結構的原理是通過犧牲面積來降低功耗。將一個功能模塊復制為n(n≥2)個相同的模塊,這些模塊并行計算后通過數據選擇器選擇輸出,采用二分頻的并行結構。

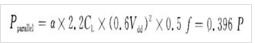

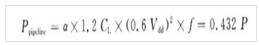

并行設計后,由于有多個模塊同時工作,提高了吞吐能力,可以把每個模塊的速度降低為原來的l/n。根據延時和工作電壓的線性關系,工作電壓可以相應降低為原來的l/n,電容增大為原來的n倍,工作頻率降低為原來的l/n,根據式(1)功耗降低為原來的1/n2。并行設計的關鍵是算法設計,一般算法中并行計算的并行度往往比較低,并行度高的算法比較難開發。例如:若原模塊的功耗為P=a×CL×V2dd×f,采用二分頻結構,由于增加了一個模塊和數據選擇器,整個電容負載為2.2CL,工作頻率為f/2,工作電壓可以降為O.6 V,則其功耗為:

由此可見,二分頻并行結構在保持原有電路性能的同時降低了60%的功耗。

流水線技術本質上也是一種并行。把某一功能模塊分成n個階段進行流水作業,每個階段由一個子模塊來完成,在子模塊之間插入寄存器,如圖5所示。若工作頻率不變,對某個模塊的速度要求僅為原來的1/n,則工作電壓可以降低為原來的1/n,電容的變化不大(寄存器面積占的比例很小),功耗可降低為原來的1/n2,面積基本不變,但增加了控制的復雜度。例如,若原模塊的功耗為P=α×C1×V2dd×f,采用流水線技術,由于增加了寄存器,整個電容負載為1.2CL,工作頻率不變,工作電壓降為0.6 V,則其功耗為:

由此可見,流水線技術能顯著降低系統功耗。

通過流水線技術和并行結構降低功耗的前提是電路工作電壓可變。如果工作電壓固定,則這兩種方法只能提高電路的工作速度,并相應地增加了電路的功耗。在深亞微米工藝下,工作電壓已經比較接近閾值電壓,為了使工作電壓有足夠的下降空間,應該降低闊值電壓;但是隨著閾值電壓的降低,亞閾值電流將呈指數增長,靜態功耗迅速增加。因此,電壓的下降空間有限。

4) 低功耗單元庫

設計低功耗單元庫是降低功耗的一個重要方法,包括調整單元尺寸、改進電路結構和版圖設計。用戶可以根據負載電容和電路延時的需要選擇不同尺寸的電路來實現,這樣會導致不同的功耗,因此可以根據需要設計不同尺寸的單元。同時,為常用的單元選擇低功耗的實現結構,如觸發器、鎖存器和數據選擇器等。

5) 低功耗狀態機編碼

狀態機編碼對信號的活動性具有重要影響,通過合理選擇狀態機狀態的編碼方法,減少狀態切換時電路的翻轉,可以降低狀態機的功耗。其原則是:對于頻繁切換的相鄰狀態,盡量采用相鄰編碼。例如:Gray碼在任何兩個連續的編碼之間只有一位的數值不同,在設計計數器時,使用Gray碼取代二進制碼,則計數器的改變次數幾乎減少一半,顯著降低了功耗;在訪問相鄰的地址空間時,其跳變次數顯著減少,有效地降低了總線功耗。

6) Cache的低功耗設計

作為現代微處理器中的重要部件,Cache的功耗約占整個芯片功耗的30%~60%,因此設計高性能、低功耗的Cach結構,對降低微處理器的功耗有明顯作用。Cache低功耗設計的關鍵在于降低失效率,減少不必要的操作。通常用來降低Cache功耗的方法有以下兩種:一種是從存儲器的結構出發,設計低功耗的存儲器,例如采用基于CAM的Cache結構;另一種是通過減少對Cache的訪問次數來降低功耗。

以上主要是從硬件的角度來實現功耗的降低。除了硬件方法,通過軟件方面的優化,也能顯著地降低功耗。例如:在Crusoe處理器中,采用高效的超長指令(VLIW)、代碼融合(Code Morphing)技術、LongRun電源管理技術和RunCooler工作溫度自動調節等創新技術,獲得了良好的低功耗效果。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助