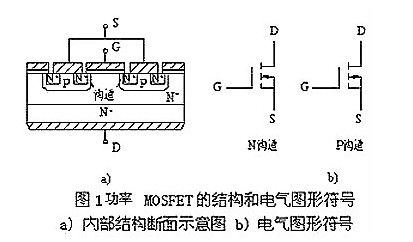

1、MOSFET的結構

MOSFET的內部結構和電氣符號如圖1所示;其導通時只有一種極性的載流子(多子)參與導電,是單極型晶體管。導電機理與小功率mos管相同,但 結構上有較大區別,小功率MOSFET管是橫向導電器件,功率MOSFET大都采用垂直導電結構,又稱為VMOSFET(Vertical MOSFET),大大提高了MOSFET器件的耐壓和耐電流能力。

按垂直導電結構的差異,又分為利用V型槽實現垂直導電的VVMOSFET和具有垂直導電雙擴散MOS結構的VDMOSFET(Vertical Double-diffused MOSFET),本文主要以VDMOS器件為例進行討論。

功率MOSFET為多元集成結構,如國際整流器公司(International Rectifier)的HEXFET采用了六邊形單元;西門子公司(Siemens)的SIPMOSFET采用了正方形單元;摩托羅拉公司 (Motorola)的TMOS采用了矩形單元按“品”字形排列。

2、MOSFET的工作原理

截止:漏源極間加正電源,柵源極間電壓為零。P基區與N漂移區之間形成的PN結J1反偏,漏源極之間無電流流過。

導電:在柵源極間加正電壓UGS,柵極是絕緣的,所以不會有柵極電流流過。但柵極的正電壓會將其下面P區中的空穴推開,而將P區中的少子—電子吸引到柵極下面的P區表面

當UGS大于UT(開啟電壓或閾值電壓)時,柵極下P區表面的電子濃度將超過空穴濃度,使P型半導體反型成N型而成為反型層,該反型層形成N溝道而使PN結J1消失,漏極和源極導電。

MOS管開關電路是利用MOS管柵極(g)控制MOS管源極(s)和漏極(d)通斷的原理構造的電路。因MOS管分為N溝道與P溝道,所以開關電路也主要分為兩種。

1、 P溝道MOS管開關電路

路編輯PMOS的特性,Vgs小于一定的值就會導通,適合用于源極接VCC時的情況(高端驅動)。需要注意的是,Vgs指的是柵極G與源極S的電壓,即柵極低于電源一定電壓就導通,而非相對于地的電壓。但是因為PMOS導通內阻比較大,所以只適用低功率的情況。大功率仍然使用N溝道MOS管。

2、 N溝道mos管開關電路

NMOS的特性,Vgs大于一定的值就會導通,適合用于源極接地時的情況(低端驅動),只要柵極電壓大于參數手冊中給定的Vgs就可以了,漏極D接電源,源極S接地。需要注意的是Vgs指的是柵極G與源極S的壓差,所以當NMOS作為高端驅動時候,當漏極D與源極S導通時,漏極D與源極S電勢相等,那么柵極G必須高于源極S與漏極D電壓,漏極D與源極S才能繼續導通。

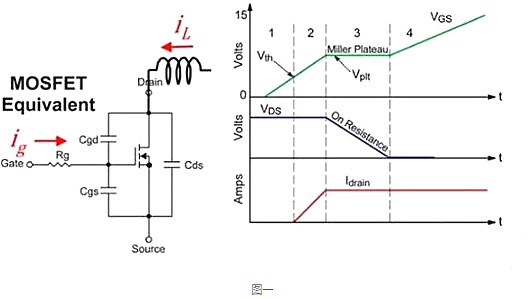

MOSFET管開關電流波形問題解析如下:

這里就用MOSFET代替BJT了,所以ids = ic,Vds=Vce,Coss也就是Cds代表輸出電容。簡單來說就是當MOS管一開始導通時輸出電容Coss還保持Vds電壓,隨著Ids電流越來越大,Vds電壓終于保持不住,開始下降。直到管子完全開啟。比較詳細的開啟過程是由Miller Plateau造成的,這里借用了網上一些解釋Miller Plateau的圖,如果有不清楚的就請見諒了。

階段1,Vgs 《 Vth,管子是關斷的,所以Ids = 0,Vds=high,ig充電Cgs。

階段2,Vgs 》 Vth,管子開啟,Ids從0增加到iL被外部電流源電感鉗住,Coss(Cds)上電壓不能突變,保持Vds。

階段3,進入Miller plateau,Vgs 》 Vth,管子仍然保持開啟,Coss開始discharge,Vds電壓開始下降,于此同時Cgd開始被ig充電。Vg保持不變。

階段4,Vd下降到接近0點,ig繼續給ig充電Cgs和Cgd充電。

階段5,Vg到達gate driver預定的電壓,管子開啟過程完成。

關斷過程和開啟過程類似,也會有Miller plateau效應。

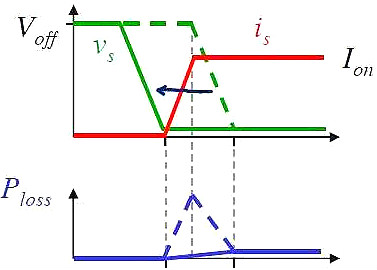

我們可以看到,如果如果MOS管開啟時VDS上有原始電壓,那么MOS開啟過程中就會有Ids和Vds的重疊,那么會帶來Switching Loss。由于Coss上的能量在極短時間內被釋放,電容上能量會損失掉(換算為Loss為0.5*Coss*Vds^2*fs),而且只要是非零電壓開啟(Non Zero Voltage Switching),會給PCB和MOS的寄生電感與電容形成的諧振腔(resonant tank)引入比較大的dv/dt或者di/dt激勵,引起比較大的ringing,甚至超過管子的額定電壓,燒毀管子。

那么我們可以避免這種情況的發生嗎?答案是可以的,也就是很多人提到的Zero Voltage Switching,雖然會付出一定的代價。我們先看如何能實現軟開關開啟Zero Voltage Switching Turn on。

實現ZVS turn on很簡單,只需要在我們開啟管子前,Vds上的電壓為零就好,這樣Ids和Vds就沒有重疊了,turn on switching loss為零,沒有high di/dt, dv/dt問題,沒有ringing,完美!那么如何實現ZVS turn on呢?個人覺得分兩種情況討論:1為PWM converter,2為resonant converter(諧振變換器)。

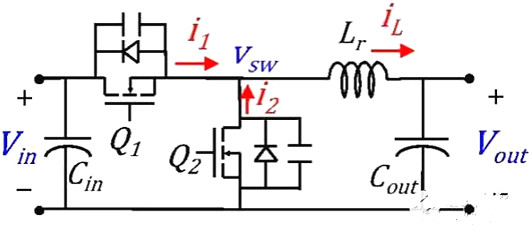

一、對于PWM converter,就拿最簡單的兩個管子的half bridge(其實也就是buck converter)做例子。

對于half bridge 實現ZVS turn on,我們希望當上管Q1開啟時電流是流進switching node (vsw)的,也就是圖中電感電流為負值,當下管Q2開啟時我們希望電流是流出switching node (vsw)的,也就是電感電流為正值。為什么這樣就可以實現ZVS turn on了呢?我們就看上管Q1開啟過程。

如果電感電流iL為負,這時候我們先關閉Q2,這時候Q1還未開啟,在這個deadTIme中iL會charge Q2的Coss,使Vsw抬高到Vin,當然不能超過Vin,因為Q1的body diode會導通,鉗位住Vsw到Vin,這時候Q1的Vds就是Vin-Vsw=0,這時候我們開啟Q1就實現ZVS了。同理對于Q2開啟時,如果電感電流為正,那么當我們首先關閉Q1管時,Vsw就會被電感電流拉低到0,因為iL》0, Q2的Coss會discharged到0,然后我們再開啟Q2,就可以達到ZVS了。

這里我有一張其他Topology的PWM converter的波形圖,也和buck工作原理類似,大概可以看看基本原理,也就是電感電流為負時,Q1可以實現ZVS,讓Vsw的ringing比較小。而當電感電流為正時,實現不了ZVS,Vsw的ringing就比較大了。

二, 對于resonant converter,其實道理類似,我們也希望在我們開啟管子前,Vds上的電壓為零。那么對于resonant converter的half bridge,我們希望看到的impedance為inducTIve,也就是感性的,這樣switching node流出的電流I就會滯后于電壓V,現在ZVS turn on。

這是因為如果電流I是滯后與電壓V的,這樣在Q1開啟之前電流I為負值就會charge Q2的Coss,同時discharge Q1的Coss,讓V到Vin,這樣Q1就實現ZVS turn on了。Q2開啟之前,電流I為正,也會discharge Q2的Coss,和charge Q1的Coss,讓V到0,這樣Q2就實現ZVS了。

總結起來,要實現ZVS turn on,對于PWM,需要電感電流為負,而且需要足夠的deadTIme;對于resonant converter,需要impedance為inducTIve,而且也需要deadtime。那么有人可能要問,對于PWM converter到底電感電流為多負?deadtime至少為多少可以保證ZVS?對于resonant converter, impedance 到底為多少?deadtime為多少可以保證ZVS?

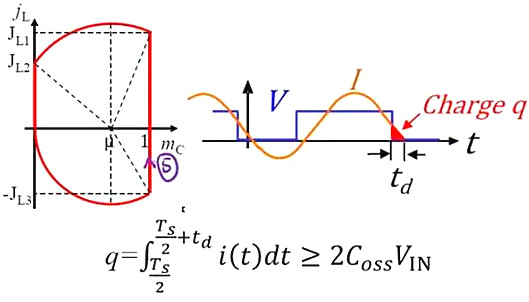

要回答這個定量問題,其實是不那么簡單的。對于PWM converter,參考quasi-square-wave

ZVS buck converters,我們是可以畫出state plane,然后根據state plane圖的幾何關系定量分析出來的,但是非常繁瑣,常常是七八個三角函數等式求解。所以我個人愚見,在設計上,就讓開關頻率小點,電感值小點,讓電感電流ripple足夠大,能達到負值就差不多了。對于resonant

converter,倒是可以簡單地通過積分方法,算出i與t的積分,讓這個it積分大于Coss上的charge就行。比如已知impedance,算出V與I的phase shift,然后換算成時間td,然后在td上對電感電流進行積分,只要這個積分大于等于Coss*Vin就行了。

說了soft switching, ZVS這么多好處,我們談談soft switching的弊端。對于PWM converter我們可以看到為了實現ZVS,我們減小了電感值,讓電感電流ripple變大,最終達到負值,實現了ZVS,但是付出的代價就是inductor current的RMS值變大,各個元器件的導通損耗(conduction loss)變大,所以我們是犧牲了conduction loss換取switching loss和小ringing。

而且如果輸出電流越大,我們需要實現ZVS的難度更大,需要進一步增大ripple,造成RMS電流進一步增大,很有可能得不償失,造成converter整體效率下降。對于resonant converter,在頻率很高的情況下,有時候需要讓impedance非常inductive,也就是I滯后于V非常厲害才能有足夠的charge q來實現ZVS,這其實也是變相降低了有功功率的傳輸,因為V和I的phase lag比較大,造成了converter的circulating current比較大,RMS電流值增大,也是增大了conduction loss。

所以在設計或者考慮ZVS等soft switching時需要對系統有個整體loss的把握,在conduction loss和switching loss之間做好trade-off,這樣才能設計出效率最高,最棒的converter。

漏極電流ID和柵源間電壓UGS的關系稱為MOSFET的轉移特性,ID較大時,ID與UGS的關系近似線性,曲線的斜率定義為跨導Gfs MOSFET的漏極伏安特性(輸出特性):截止區(對應于GTR的截止區);飽和區(對應于GTR的放大區);非飽和區(對應于GTR的飽和區)。

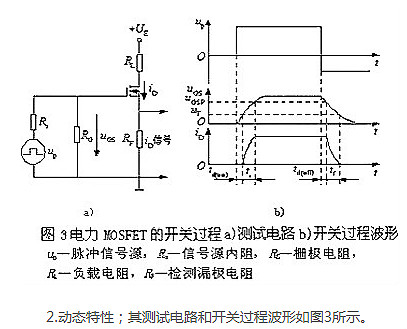

電力 MOSFET工作在開關狀態,即在截止區和非飽和區之間來回轉換。電力MOSFET漏源極之間有寄生二極管,漏源極間加反向電壓時器件導通。電力 MOSFET的通態電阻具有正溫度系數,對器件并聯時的均流有利。

開通過程;開通延遲時間td(on) —up前沿時刻到uGS=UT并開始出現iD的時刻間的時間段;

上升時間tr— uGS從uT上升到MOSFET進入非飽和區的柵壓UGSP的時間段;iD穩態值由漏極電源電壓UE和漏極負載電阻決定。UGSP的大小和iD的穩態值有關,UGS達到UGSP后,在up作用下繼續升高直至達到穩態,但iD已不變。開通時間ton—開通延遲時間與上升時間之和。

關斷延遲時間td(off) —up下降到零起,Cin通過Rs和RG放電,uGS按指數曲線下降到UGSP時,iD開始減小為零的時間段。下降時間tf— uGS從UGSP繼續下降起,iD減小,到uGS關斷時間toff—關斷延遲時間和下降時間之和。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助