MOS管,MOS管邏輯電路

邏輯電路

邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數字信號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”電路和“非門”電路組成,其輸出值僅依賴于其輸入變量的當前值,與輸入變量的過去值無關—即不具記憶和存儲功能;后者也由上述基本邏輯門電路組成,但存在反饋回路—它的輸出值不僅依賴于輸入變量的當前值,也依賴于輸入變量的過去值。由于只分高、低電平,抗干擾力強,精度和保密性佳。廣泛應用于計算機、數字控制、通信、自動化和儀表等方面。最基本的有與電路、或電路和非電路。

MOS管邏輯電路解析

MOS管構成的各種基本MOS管邏輯電路必須熟記于心,才能夠更熟練的看懂芯片的框圖。場效應管(Field-Effect Transistor)通過不同的搭配可以構成各種各樣的門電路,如開篇所說,這些最基本的單元電路或許是現代IC的基礎。以下的電路形式在常用的74系列的芯片中大量存在著,之后介紹的OD門,緩沖器則常見于芯片的GPIO口等管腳的設計。

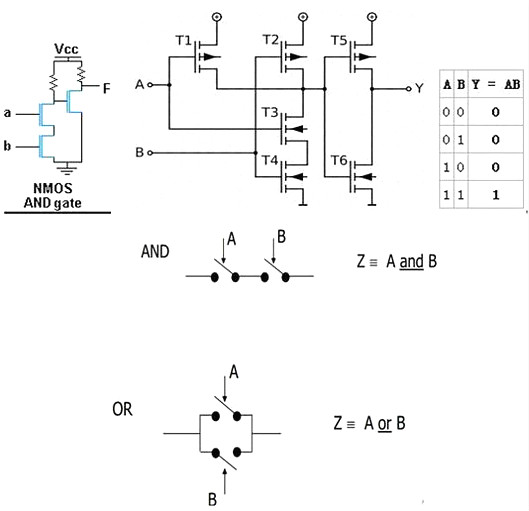

(一)MOS管邏輯電路-MOS管構成的與門、或門電路

與門可以由六個管子構成,通過示意圖應該能更清楚看出與門的工作示意圖,然后由真值表可以看出輸入輸出的對應關系。本文中給出與門的對應電路,如有興趣,大家可以思考或門的電路結構,其實二者是存在對應關系的。

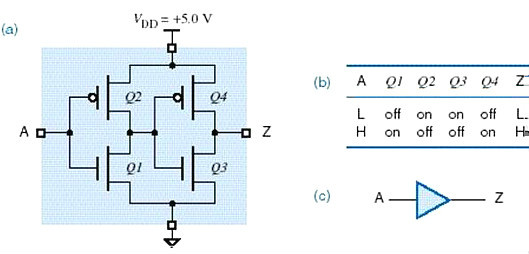

(二)反相器

下圖則給出了反相器的電路圖,輸入和輸出狀態相反,謂之反相器。

電路分析:

輸入Vi為低電平時,上管導通,下管截止,輸出為高電平;輸入Vi為高電平時,上管截止,下管導通,輸出為低電平。

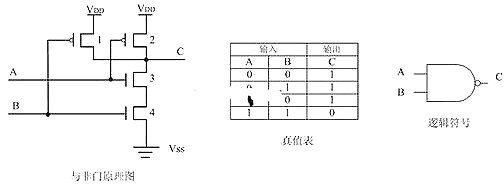

(三)與非門

下圖則給出了與非門的電路圖,與非門也就是同為零,異為一。

當A,B輸入均為低電平時,1,2管導通,3,4管截止,C端電壓與Vdd一致,輸出高電平。當A輸入高電平,B輸入低電平,1,3管導通,2,4管截止,C端電位與1管的漏極保持一致,輸出高電平。當A輸入低電平,B輸入高電平,2,4導通,1,3管截止,C端電位與2管的漏極保持一致,輸出高電平。當A,B輸入均為高電平時,1,2管截止,3,4管導通,C端電壓與地一致,輸出低電平。

(四)緩沖器Buffer

CMOS緩沖器(buffer),緩沖器跟反相器是對立的,緩沖器輸入與輸出相同,反相器輸入與輸出相反。

電路分析:

前面一級Q1,Q2組成了一個反相器;后面一級Q3,Q4又構成了一個反相器,相當于反了兩次相,于是又還原了。

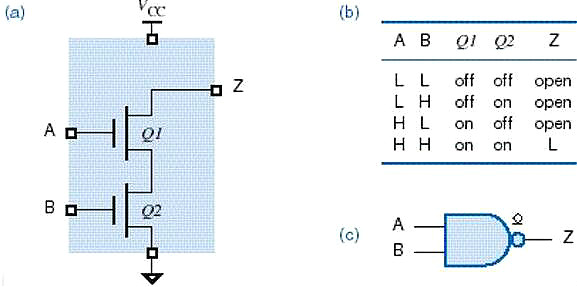

(五)漏極開路門

漏極開路門是一個十分經典常用的電路,常見于主芯片的GPIO口或者單片機的GPIO口的設計中。要最重要的一點就是:漏極開路是高阻態,一般應用需要接上拉電阻。

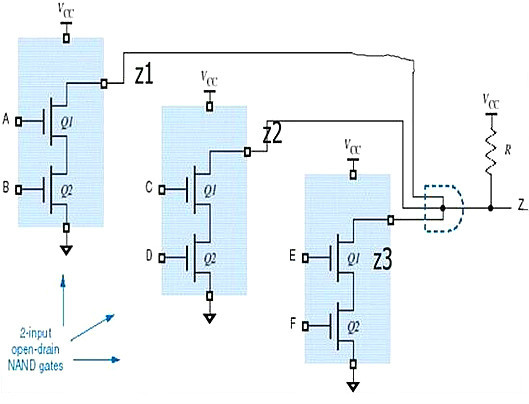

【漏極開路門的應用-線與邏輯】Z=z1z2z3

“線與”邏輯是因為多個邏輯單元的輸出的三極管,共用一個上拉電阻,只要一個邏輯單元輸出低電平,即集電極(漏極)開路輸出的管子導通,那么輸出低電平;而只有全部單元截止,輸出端被上拉電阻置為高電平,這是一個很實用的電路,可以用于邏輯仲裁等電路系統中。

MOS管邏輯電路-組合邏輯電路分析方法

在asic設計和pld設計中組合邏輯電路設計的最簡化是很重要的,在設計時常要求用最少的邏輯門或導線實現。在asic設計和pld設計中需要處理大量的約束項,值為1或0的項卻是有限的,提出組合邏輯電路設計的一種新方法。與邏輯表示只有在決定事物結果的全部條件具備時,結果才發生的因果關系。輸出變量為1的某個組合的所有因子的與表示輸出變量為1的這個組合出現、所有輸出變量為0的組合均不出現,因而可以表示輸出變量為1的這個組合。

組合邏輯電路的分析分以下幾個步驟:

(1)有給定的邏輯電路圖,寫出輸出端的邏輯表達式;

(2)列出真值表;

(3)通過真值表概括出邏輯功能,看原電路是不是最理想,若不是,則對其進行改進。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助